Y. Triatouhas

**Dept. of Computer Science and Engineering**

# **CMOS Integrated Circuit Design Techniques**

#### **Overview**

- 1. Dynamic power consumption reduction

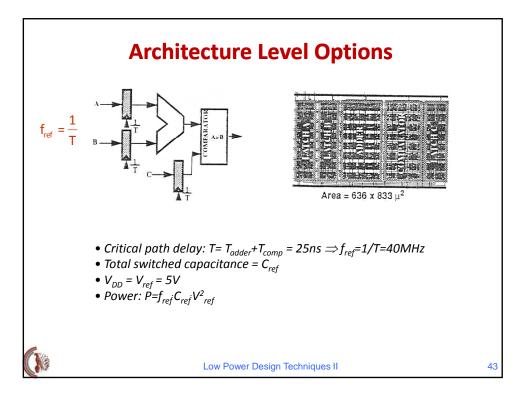

- 2. Architecture level power reduction

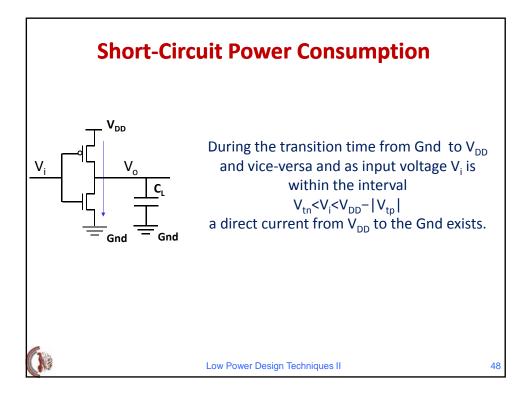

- 3. Short circuit power consumption reduction

VLSI Systems and Computer Architecture Lab

Low Power Design Techniques II

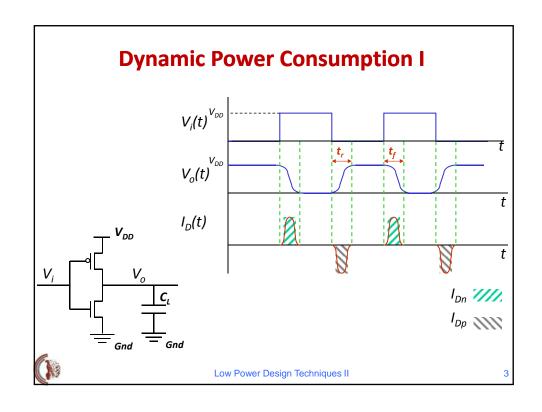

#### **Dynamic Power Consumption Reduction**

Low Power Design Techniques II

5

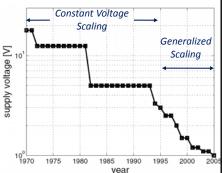

## **Technology Scaling**

- A new CMOS technology every 2-3 years.

- Technology scales down by a factor κ=1/α≈0.7

$$\begin{split} &\blacktriangleright W=\kappa W, \qquad \qquad L=\kappa L \\ &\blacktriangleright V_{DD}=\kappa V_{DD}, \qquad V_{th}=\kappa V_{th} \\ &\blacktriangleright t_{ox}=\kappa t_{ox} \\ &\blacktriangleright C_{ox}=\epsilon_{ox} / t_{ox}=C_{ox} / \kappa \\ &\blacktriangleright I_D=\mu_D C_{ox} W / L (V_{DD}-V_{th})^2=(1/\kappa)(\kappa/\kappa)(\kappa)^2 I_D=\kappa I_D \\ &\blacktriangleright C_{gate}=C_{ox} W L=(1/\kappa)(\kappa)(\kappa)C_{gate}=\kappa C_{gate} \\ &\blacktriangleright C_{wire}~(\infty~L)=\kappa C_{wire} \end{split}$$

- Delay =  $CV_{DD} / I_D = (\kappa \cdot \kappa / \kappa)$ Delay =  $\kappa$ Delay

- Energy =  $CV_{DD}^2 = \kappa^3 Energy$

- Power = Energy / Delay = κ<sup>2</sup>Power

- Energy × Delay =  $\kappa^4$  (Energy × Delay)

Low Power Design Techniques II

## **Power Supply V<sub>DD</sub> Reduction**

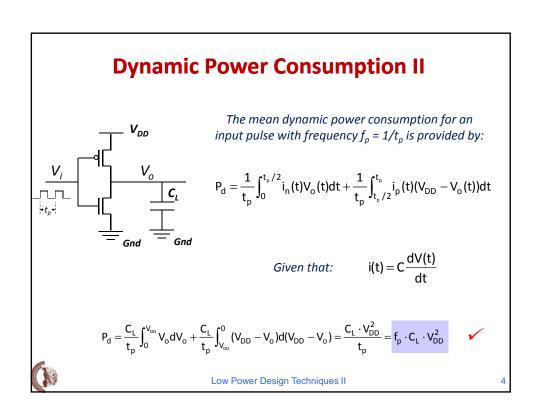

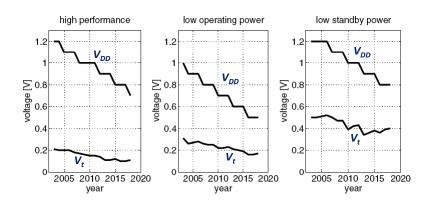

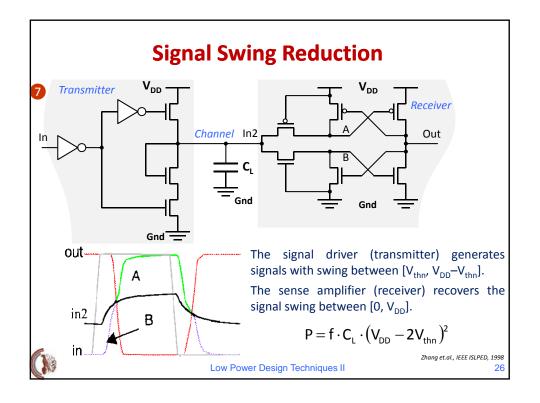

Since:  $P_d = f_p \cdot C_L \cdot V_{DD}^2$  the reduction of  $V_{DD}$  will result in significant power consumption reduction (square low).

<u>However</u>, the power supply reduction will result in the increment of the circuit signal propagation delays. To confront with this drawback, the following techniques are proposed:

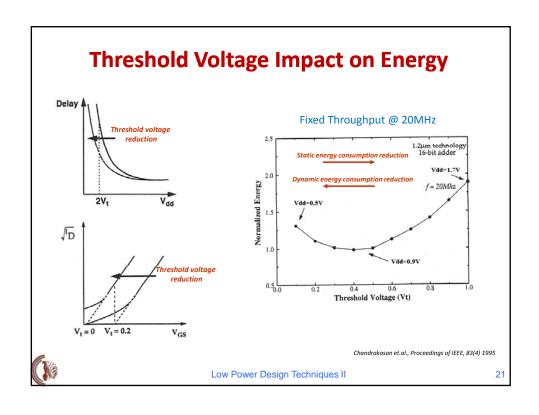

- ullet Threshold voltage  $V_{th}$  reduction (but static power is increased).

- Use of reduced threshold voltage  $V_{th}$  only for the gates at time (performance) critical signal paths in the circuit.

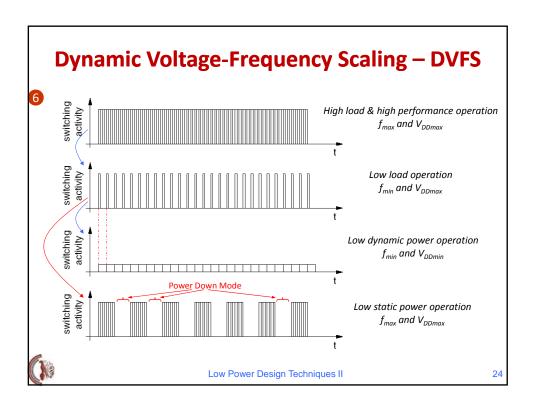

- ullet Use of multi power supplies or an adaptive power supply  $V_{\rm DD}$ .

- Exploitation of pipeline design techniques or other parallelism design schemes for the reduction of the signal propagation delay.

Low Power Design Techniques II

7

# **V**<sub>DD</sub> – **V**<sub>t</sub> Scaling Scenarios

Low Power Design Techniques II

# **V<sub>DD</sub> Reduction and Performance**

| device/circuit parameter | constant voltage<br>scaling | constant field<br>scaling | generalized scaling 1/\alpha             |  |

|--------------------------|-----------------------------|---------------------------|------------------------------------------|--|

| channel length           | $1/\alpha$                  | $1/\alpha$                |                                          |  |

| channel width            | $1/\alpha$                  | $1/\alpha$                | $1/\alpha$                               |  |

| oxide thickness          | 1/α                         | $1/\alpha$                | $1/\alpha$                               |  |

| area per device          | $1/\alpha^2$                | $1/\alpha^2$              | $1/\alpha^2$                             |  |

| terminal voltages        | 1                           | $1/\alpha$                | $\epsilon/\alpha$                        |  |

| threshold voltage        | 1                           | $1/\alpha$                | $\epsilon/\alpha$                        |  |

| internal electric fields | α                           | 1                         | $\epsilon$                               |  |

| doping                   | $\alpha^2$                  | α                         | $\epsilon \alpha$                        |  |

| saturation current       | α                           | $1/\alpha$                | $\epsilon/\alpha$                        |  |

| gate capacitance         | $1/\alpha$                  | $1/\alpha$                | $1/\alpha$                               |  |

| gate delay               | $1/\alpha^2$                | $1/\alpha$                | $1/\alpha$                               |  |

| power dissipation        | α                           | $1/\alpha^2$              | $\epsilon^2/\alpha^2$                    |  |

| power density            | $\alpha^3$                  | 1                         | $\frac{\epsilon^2/\alpha^2}{\epsilon^2}$ |  |

| power delay product      | $1/\alpha$                  | $1/\alpha^3$              | $\epsilon^2/\alpha^3$                    |  |

$\alpha$  is the scaling factor while  $\alpha/\epsilon$  is the reduced scaling factor

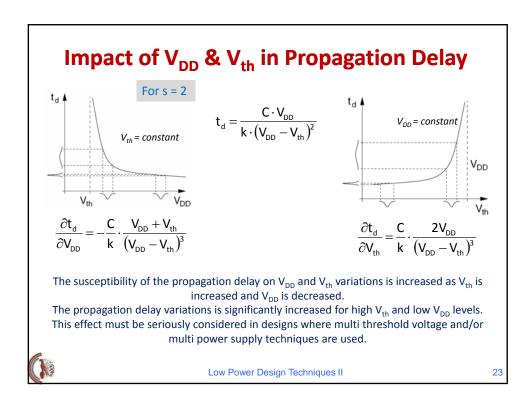

Influence of  $V_{DD}$  on the current  $I_{D}$  and propagation delay  $t_{d}$ :

$$I_D = k \cdot (V_{DD} - V_{th})^s$$

$$t_d = \frac{C \cdot V_{DD}}{k \cdot (V_{DD} - V_{th})^s}$$

where s is the velocity saturation index (1 < s < 2).

Low Power Design Techniques II

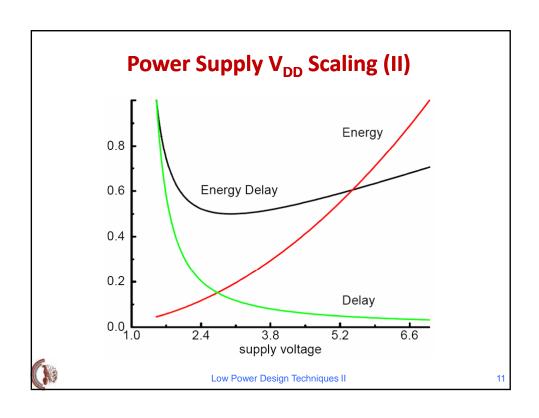

# Power Supply V<sub>DD</sub> Scaling (I)

#### **Propagation Deley**

$$t_d = \frac{C \cdot V_{DD}}{I_D}$$

$$I_{_D} = k \cdot (V_{_{DD}} - V_{_{th}})^2$$

$$t_{d} = \frac{C \cdot V_{DD}}{k \cdot (V_{DD} - V_{th})^{2}}$$

$$E = C \cdot V_{DD}^2$$

### Metric

Energy

$$\times$$

Delay

$$E = C \cdot V_{DD}^{2}$$

$$E \cdot t_{d} = \frac{C^{2} \cdot V_{DD}^{3}}{k \cdot (V_{DD} - V_{th})^{2}}$$

$$E \cdot t_{d} = \gamma \frac{V_{DD}^{3}}{\left(V_{DD} - V_{th}\right)^{2}}$$

#### Metric Minimization

$$\frac{d(E \cdot t_{d})}{dV_{DD}} = \gamma \frac{(V_{DD} - V_{th})^{2} \cdot 3 \cdot V_{DD}^{2} - V_{DD}^{3} \cdot 2 \cdot (V_{DD} - V_{th})}{(V_{DD} - V_{th})^{4}} \Longrightarrow$$

$$\frac{d(E \cdot t_{d})}{dV_{DD}} = \gamma \frac{V_{DD}^{2}(V_{DD} - 3V_{th})}{(V_{DD} - V_{th})^{3}}$$

The derivative is vanished for  $V_{DD} = 3V_{th}$

Low Power Design Techniques II

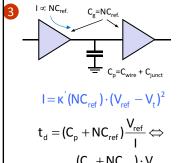

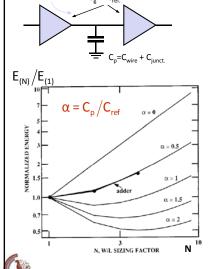

$$t_{d} = \kappa \frac{(C_{p} + NC_{ref}) \cdot V_{ref}}{(NC_{ref}) \cdot (V_{ref} - V_{t})^{2}} \Leftrightarrow$$

$$t_d = \kappa (1 + \alpha/N) \frac{V_{ref}}{(V_{ref} - V_t)^2}$$

$$\alpha = C_{p}/C_{ref}$$

Let us consider a reference design with transistor sizes W/L so that the input (transistor gate related) capacitance is  $C_{\rm ref}$ .

Initially, the power supply is V<sub>ref</sub>

Aiming to reduce the dynamic power consumption, we reduce the power supply voltage to  $V_{\rm N}$ .

This will result in the increment of the propagation delay time of the circuit.

In order to recover the operating speed, we decide to increase (scale up) the transistor sizes in the design by a factor N

(our target is to reduce the propagation –  $t_d \downarrow$ ).

Is this approach applicable and if yes which is the proper N factor?

Chandrakasan et.al., IEEE J. Solid-State Circuits, 27(4) 1992

Low Power Design Techniques II

## **Transistor Size Scaling (II)**

$I \propto NC_{ref.}$

For each N value, there is a proper power supply voltage  $V_{\rm N}$  where both designs (the reference & the scaled one) exhibit the same speed performance.

Given that the propagation delay  $t_d$  increases with  $1/V_{ref}$  ( $V_{th} <<$ )\*, the  $V_N$  voltage for which the  $t_d$  of the scaled design is equal to this of the reference design (N=1), is provided by:

$$\begin{split} V_N &= \frac{(1+\alpha/N)}{1+\alpha} V_{ref} & \underset{(N>1)}{\leq} V_{ref} \\ & t_{_d} \approx \kappa (1+\alpha) \frac{1}{V_{_{ref}}} = \kappa (1+\alpha/N) \frac{1}{V_{_N}} \end{split}$$

Consequently, for every N, the energy consumption at the first stage is given by:

$$E(N) = (C_p + NC_{ref})V_N^2 = \frac{NC_{ref}(1 + \alpha/N)^3}{(1 + \alpha)^2}V_{ref}^2$$

Low Power Design Techniques II

15

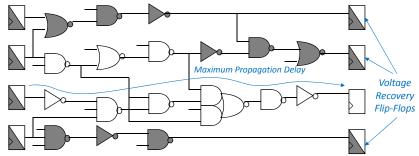

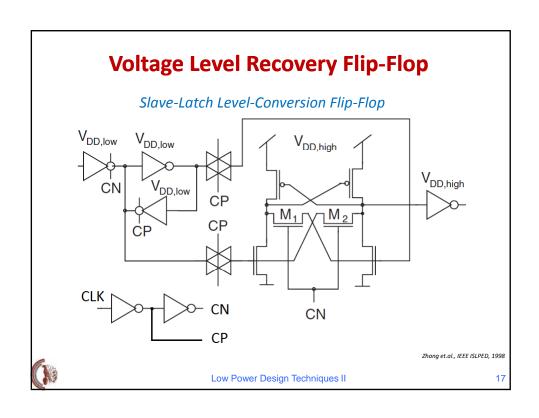

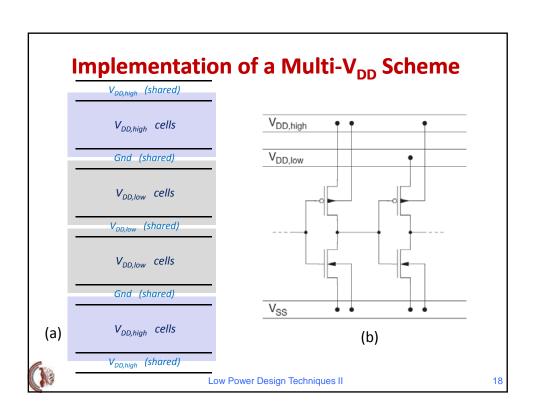

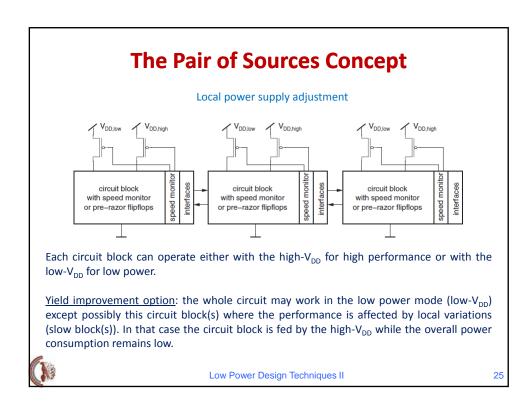

## **Multiple Power Supplies**

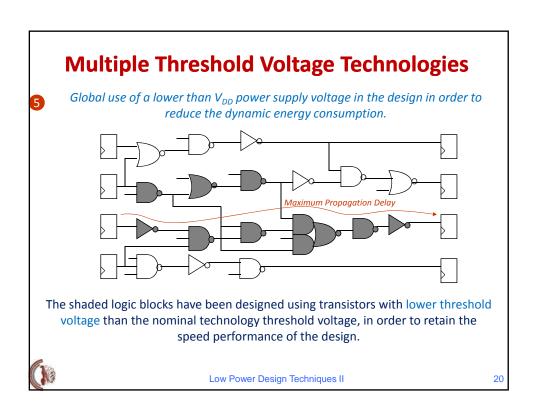

Selective use of a lower than  $V_{\rm DD}$  power supply voltage in order to reduce the dynamic power consumption.

Use of a single threshold voltage  $V_{\it th}$  for the transistors in the design

The shaded logic gates are fed with a lower voltage  $V_L$ . The shaded Flip-Flops recover the signal voltage level  $V_H \equiv V_{DD}$  at the output.

Note that when a logic block is fed with a lower than  $V_{DD}$  voltage, then every subsequent block up to the recovery Flip-Flops must be fed with the same voltage level.

Low Power Design Techniques II

Low Power Design Techniques II

19

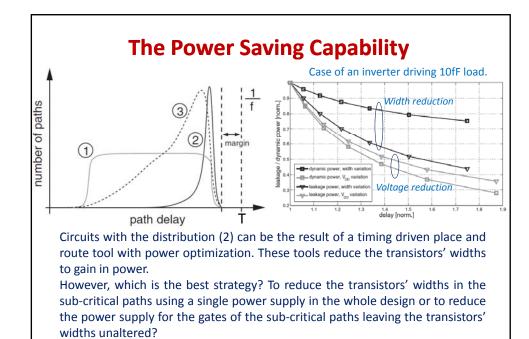

The second approach seems to provide better results!

# **V**<sub>th</sub> Reduction Issues

- Static power consumption increment of the weak-inversion (subthreshold) leakage current.

- Circuit operation susceptibility on the V<sub>th</sub> variations.

#### Demand for:

- $\succ$  increased threshold voltage  $V_{th}$  at the idle (stand-by) state

- $\succ$  adaptable threshold voltage  $V_{th}$  at the normal mode of operation by adjusting the substrate bias.

Dynamic & static power consumption reduction techniques

|                          | Active                  | Stand-by                       |

|--------------------------|-------------------------|--------------------------------|

| Multiple V <sub>th</sub> | Dual-V <sub>th</sub>    | MTCMOS                         |

| Variable V <sub>th</sub> | V <sub>th</sub> hopping | VTCMOS                         |

| Multiple V <sub>DD</sub> | Dual-V <sub>DD</sub>    | Reverse V <sub>GS</sub> switch |

| Variable V <sub>DD</sub> | V <sub>DD</sub> hopping |                                |

Low Power Design Techniques II

## **Energy Consumption (I)**

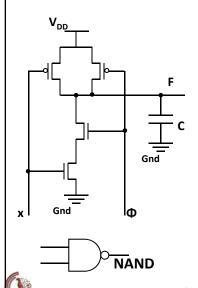

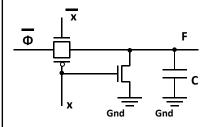

The required charge Q in order to charge the output node F (x="1",  $\Phi$ ="0") is given by the next equation :

$$Q = CV_{DD}$$

(1)

The required energy from the power supply is:

$$E = QV_{DD} = CV_{DD}^2$$

(2)

Considering that the conducting pMOS transistor and the capacitance C form an RC network, the charging current as a function of time is:

$$i(t) = \frac{dq}{dt} = \frac{V_{DD}}{R} e^{-\frac{t}{RC}}$$

(3)

Low Power Design Techniques II

29

## **Energy Consumption (II)**

The instantaneous power dissipation in the pMOS transistor is:

$$P(t) = i^{2}(t)R = \frac{V_{DD}^{2}}{R}e^{-\frac{2t}{RC}}$$

(4)

The energy dissipation within a time duration T in order to charge the output node, is given by:

$$E_{diss-p} = \int_{0}^{T} P(t) dt = \int_{0}^{T} \frac{V_{DD}^{2}}{R} e^{-\frac{2t}{RC}} dt = \frac{1}{2} C V_{DD}^{2} \left( 1 - e^{-\frac{2T}{RC}} \right) = \frac{1}{2} C V_{DD}^{2} \bigg|_{T \to \infty}$$

(5)

Consequently, the energy stored on C is provided by the following difference:

$$E_{bit} = E - E_{diss-p} = CV_{DD}^2 - \frac{1}{2}CV_{DD}^2 = \frac{1}{2}CV_{DD}^2$$

(6)

Low Power Design Techniques II

## **Energy Consumption (III)**

In the next transition of the clock signal  $\Phi$  (x="1",  $\Phi$ ="1") the stored energy on C will change from  $E_{bit}$  to 0 and the difference between the initial and the final energy is dissipated on the equivalent resistances of the nMOS transistors that discharge the output node. Thus, the total energy dissipation in a clock cycle is:

$$E_{cycle} = E_{diss-p} + E_{diss-n} = \frac{1}{2}CV_{DD}^2 + \frac{1}{2}CV_{DD}^2 = CV_{DD}^2 = 2E_{bit} = E$$

(7)

Consequently, the energy that is recovered back to the power supply within a clock cycle is zero (0):

$$E_{rtn} = 0$$

Low Power Design Techniques II

31

## **Energy Recovery Principle (I)**

The previous discussion shows that during the charging of a node, the current asymptotically approaches 0 and the energy dissipation asymptotically approaches  $CV^2_{DD}/2$ . After a time duration of 3RC the output voltage is at the 95% of its final voltage, the current is less than 5% of its initial value and the energy dissipation is at the 97.5% of its final value. Thus, after another 3RC time duration the circuit has almost reached its final state, so that for a total time interval of 6RC the transition is considered completed.

Let us replace the power supply with a "step" voltage, where for the time interval from 0 to 3RC the voltage level is  $V_{DD}/2$  and from 3RC to 6RC the voltage level is  $V_{DD}$ . Then, the energy dissipation will be:

$$E_{diss-p} = \int_0^{3RC} P(t)dt + \int_{3RC}^{6RC} P(t)dt \approx \frac{1}{2}C\left(\frac{V_{DD}}{2}\right)^2 + \frac{1}{2}C\left(\frac{V_{DD}}{2}\right)^2 = \frac{1}{4}CV_{DD}^2$$

(8)

Low Power Design Techniques II

## **Energy Recovery Principle (II)**

According to the previous analysis, "stepwise" voltage power supplies with more than two steps can be used in order to reduce further the energy dissipation.

The next idea, is to consider a power supply that continuously varies (from  $0\rightarrow V_{DD}$ ) so that the charging current remains constant throughout the entire process:

$$i(t) = \frac{Q}{T} = \frac{CV}{T}$$

(9)

Then, the charging energy dissipation will be:

$$E_{diss-p} = \int_0^T i^2(t) R dt = R \int_0^T \left( \frac{CV_{DD}}{T} \right)^2 dt = \frac{RC}{T} CV_{DD}^2$$

(10)

Low Power Design Techniques II

31

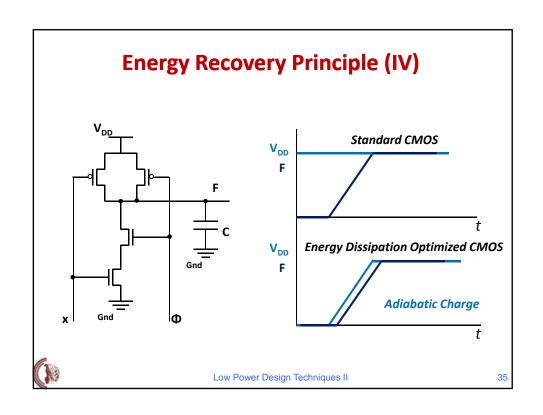

## **Energy Recovery Principle (III)**

The same situation can take place during the discharging phase by continuously varying the Gnd power supply from  $V_{DD} \rightarrow 0$ , so that the current remains constant. Thus, again the energy dissipation on the nMOS transistor will be:

$$E_{diss-n} = \frac{RC}{T}CV_{DD}^2 \tag{11}$$

Consequently, the total energy dissipation turns to be :

$$E_{diss} = E_{diss-p} + E_{diss-n} = 2\frac{RC}{T}CV_{DD}^{2}$$

(12)

By selecting a proper T, the total energy dissipation can be less than the energy delivered within a cycle when constant power supplies are used :  $E=2E_{bit}=CV^2_{DD}$ . The difference in the energy is:

$$\Delta E = CV_{DD}^{2} - 2\frac{RC}{T}CV_{DD}^{2} > 0|_{T>2RC}$$

(13)

Low Power Design Techniques II

### Adiabatic NOT gate

A possible solution in order to exploit the energy recovery principle is to replace the power supply  $V_{DD}$  with the clock signal  $\Phi$ . This is a *power-clock*.

Provided that the power-clock is dynamically adjusted to the constant current requirement an adiabatic charging is achieved and the energy dissipation follows equation (10).

Low Power Design Techniques II

# **Algorithm Selection**

#### **Video Compression**

| Video compression                |                     |                    |                      |  |  |

|----------------------------------|---------------------|--------------------|----------------------|--|--|

| DCT Algorithm                    | Multiplies<br>(8x8) | Additions<br>(8x8) | Implemented by       |  |  |

| Brute Force                      | 4096                | 4096               |                      |  |  |

| Row-Col DCT                      | 1024                | 1024               | Bell core (16x16)    |  |  |

| Chen's Algorithm                 | 256                 | 416                | Telettra             |  |  |

| Lee's Algorithm                  | 192                 | 464                | SGS - Thompson       |  |  |

| Feig's Algorithm<br>(scaled DCT) | 54                  | 462                | IBM<br>(GP computer) |  |  |

Algorithm complexity

By reducing the number of tasks (circuit activity) the energy dissipation is reduced.

Low Power Design Techniques II

### References

- "Low Power Design Methodologies," J. Rabaey and M. Pedram, Springer, 1997.

- "Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies," S. Henzler, Springer, 2006.

- "Low-Power Digital VLSI Design," A. Bellaouar and M. Elmasry, Kluwer Academic Publishers, 1996.

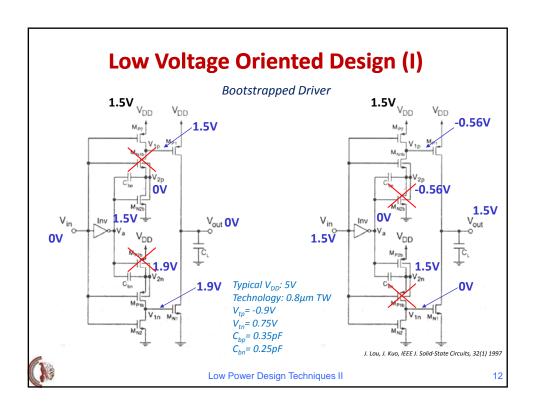

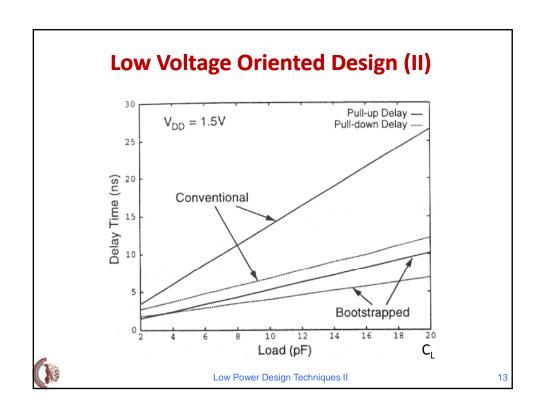

- "A 1.5V Full-Swing Bootstrapped CMOS Large Capacitive-Load Driver Circuit Suitable for Low-Voltage CMOS VLSI," J. Lou and J. Kuo, IEEE Journal of Solid-State Circuits, vol. 32, no. 1, pp. 119-121, 1997.

- "A 0.9-V, 150-MHz, 10-mW, 4 mm, 2-D Discrete Cosine Transform Core Processor with Variable Threshold-Voltage (VT) Scheme," T. Kuroda et.al., IEEE Journal of Solid-State Circuits, vol. 31, no. 11, pp. 1770-1779, 1996.

- "Low-Power CMOS Digital Design," A. Chandrakasan, S. Sheng and R. Brodersen, IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, 1992.

- "Minimazing Power Consumption in Digital CMOS Circuits," A. Chandrakasan, R. Brodersen, Proceedings of the IEEE, vol. 83, no. 4, pp. 498-523, 1995.

Low Power Design Techniques II