# **CMOS Integrated Circuit Design Techniques**

#### **Overview**

- 1. Power consumption sources

- 2. Static power consumption reduction

VLSI Systems and Computer Architecture Lab

Low Power Design Techniques I

## **Power Consumption**

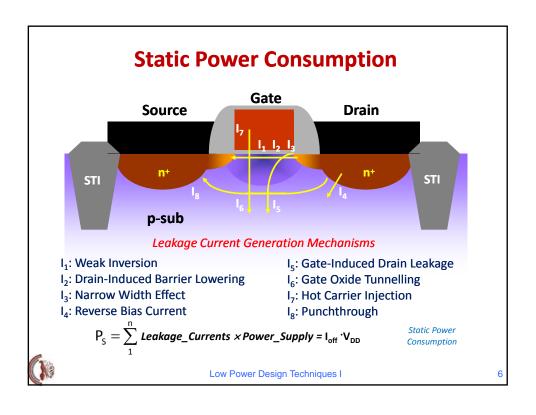

We distinguish three power consumption sources in digital integrated circuits:

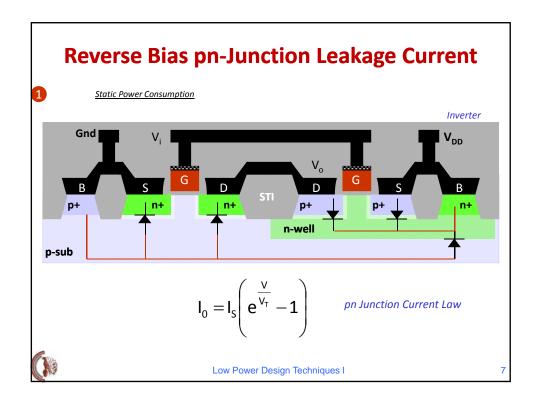

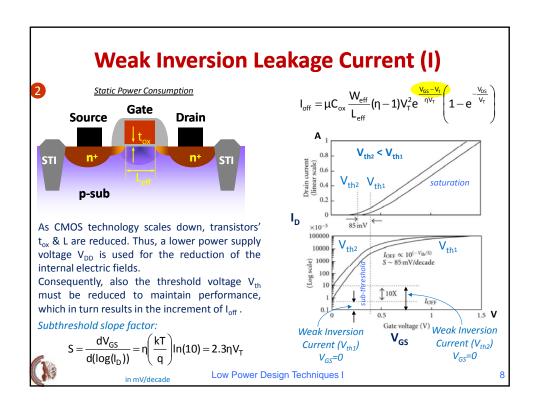

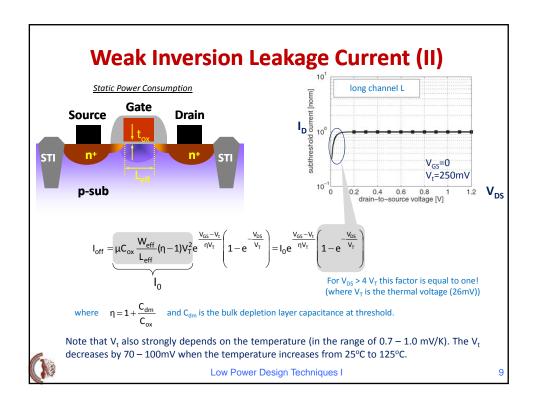

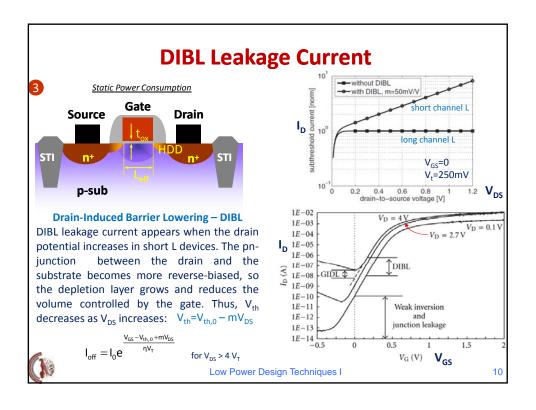

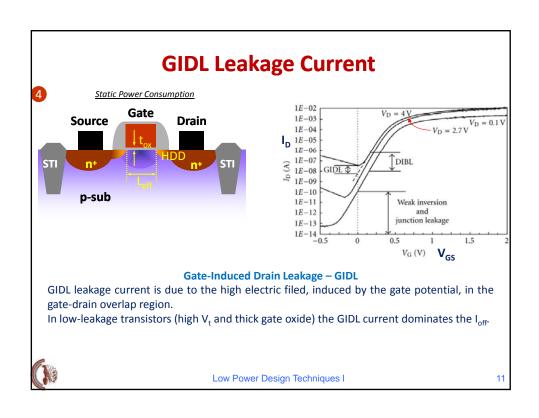

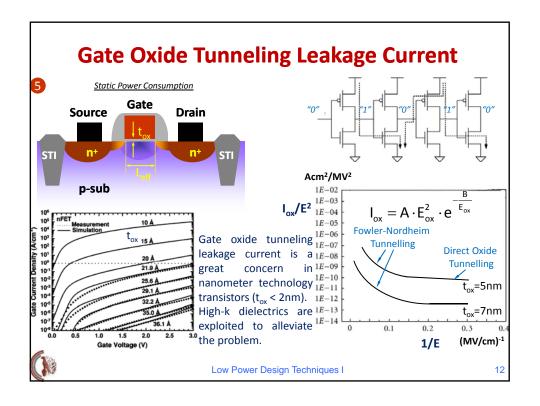

- Static power consumption: due to leakage currents in the circuit, it remains even when the circuit is inactive (idle state).

- Dynamic power consumption: due to charging and discharging of circuit's internal node parasitic capacitances.

- Short-circuit power consumption: due to short-circuit currents between the power supplies during signal transitions at the inputs of the logic gates.

$$P = V_{DD} \cdot I_{leakage}(V_{DD}) + f_{clk} \cdot \alpha \cdot C_{tot} \cdot V_{DD}^2 + V_{DD} \cdot I_{sc}(V_{DD})$$

Low Power Design Techniques I

#### **Static Power Consumption Reduction**

Low Power Design Techniques I

13

## **Power Gating**

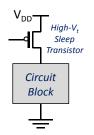

In power gating we use of a switch device (sleep transistor) between the circuit block and the power supply  $(V_{DD}, Gnd)$ , aiming to reduce the static power during the idle system states (sleep states).

#### Trade-offs arise between:

- The maximum delay degradation.

- The requested leakage reduction ratio (LRR).

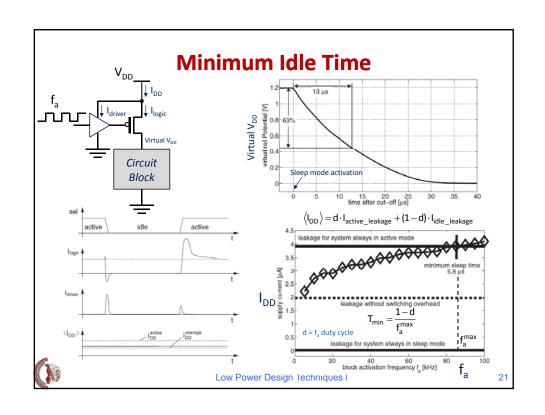

- The minimum effective power down time (T<sub>min</sub>).

- The cost.

#### Design constraints:

- The area overhead, which affects cost and yield.

- The maximum acceptable delay overhead.

- The standby-power specifications that must consider the standby-time of the system.

- The switch (sleep) transistor type and the available options for the standard cells.

Low Power Design Techniques I

### **Properties of Power Gating**

- High leakage reduction ratio.

- Small impact on performance in active mode.

- Small area overhead due to the: switches, control logic, drivers ...

- Independent power gating for different circuit blocks cores.

- Fast sleep-in and sleep-out periods with small energy overhead.

- Multiple sleep states.

#### Side Effects:

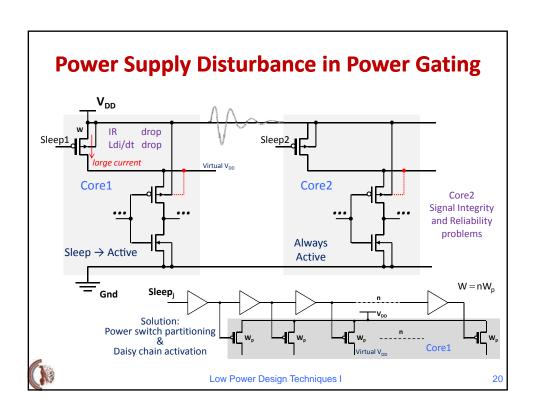

- The influence of surrounding active blocks by the fast activation of a large block from its sleep mode. Aiming to alleviate this, usually a latency is introduced which increases  $T_{\min}$ .

- The need to retain the internal states during the sleep mode.

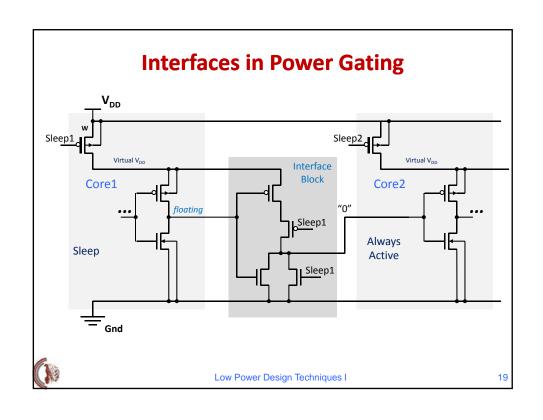

- Block interfaces are required between active and inactive blocks.

- Idle time statistics must be exploited to predict block activation and proper control logic must be implemented for the activation task. This will increase power and consequently  $T_{\min}$ .

Low Power Design Techniques I

15

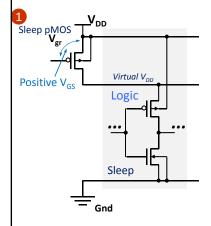

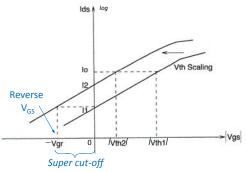

## Power Gating with a Reverse V<sub>GS</sub> Switch

In active mode a gate voltage V<sub>G</sub> lower than 0 is used (boosted gate) aiming to maintain performance.

In sleep mode a gate voltage V<sub>G</sub> higher than V<sub>DD</sub> is used for I<sub>off</sub> reduction.

Low Power Design Techniques I

.

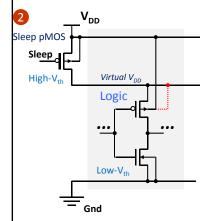

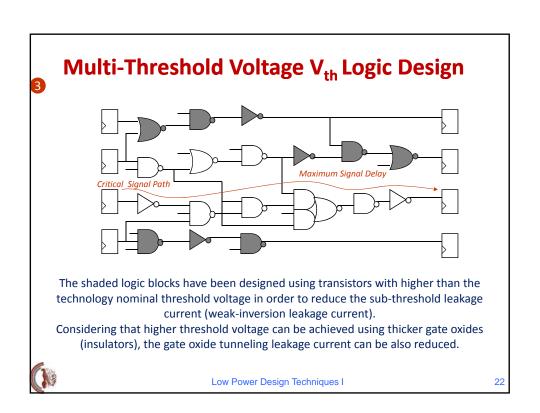

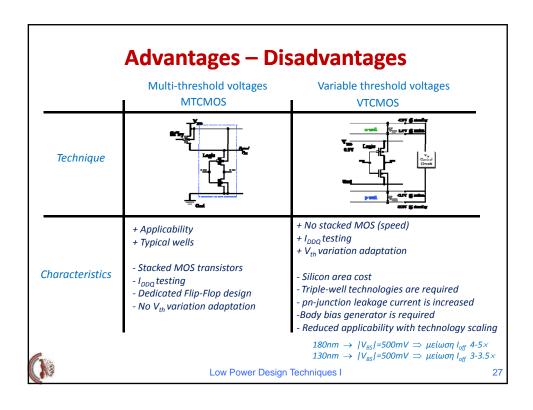

Multiple threshold voltage CMOS (MTCMOS) technology

$$I_{off} = \mu C_{ox} \frac{W_{eff}}{L_{eff}} (\eta - 1) V_{T}^{2} e^{\frac{V_{SG} - |V_{thp}|}{\eta V_{T}}} \left( 1 - e^{-\frac{V_{SD}}{V_{T}}} \right)$$

A transistor with higher threshold voltage (e.g. a double gate oxide transistor) is used between the logic circuit and the power supply. In the idle mode of operation this transistor is switched to the cutoff region (sleep mode) by exploiting a dedicated signal (*Sleep*).

Thus, leakage currents due to weak inversion and gate oxide tunneling can be exponentially decreased.

$$\begin{split} V_{th} &= V_{th0} \pm \gamma \! \left( \! \sqrt{ \left| (-2) \varphi_{\scriptscriptstyle F} + V_{SB} \right| } - \sqrt{ \left| 2 \varphi_{\scriptscriptstyle F} \right| } \right) \\ \gamma &= \frac{t_{ox}}{\epsilon_{ox}} \sqrt{ 2 q \epsilon_{Si} N} \end{split}$$

Low Power Design Techniques I

17

### **Threshold Voltage Increase vs Area Overhead**

10

A high- $V_t$  transistor is desirable due to the exponential impact of  $V_t$  on subthreshold currents. However, the on-resistance of the transistor will be larger.

The latter can be compensated by a larger transistor width W, which in turn will increase area overhead and also will increase linearly the subthreshold current. The selection of W with respect to  $V_t$  is crucial!

For a desired on-current  $I_D$  it stands that:

$$I_{D} = \mu C_{ox} \frac{W}{L} \left[ (V_{DD} - V_{t}) V_{DSmax} - \frac{V_{DSmax}^{2}}{2} \right]$$

where  $|V_{GS}|=V_{DD}$  and  $|V_{DS}|=V_{DSmax}$  which is the max  $V_{DS}$  that guarantees the required switching speed of the logic.

$$W(V_t) = \frac{I_D L}{\mu C_{ox}} \left[ (V_{DD} - V_t) V_{DSmax} - \frac{V_{DSmax}^2}{2} \right]^{-1}$$

Inserting this W in the  $I_{\rm off}$  equation the side graph is drawn. The area overhead grows rapidly while the subthreshold current decreases monotonously!

$\rm V_{t}$  is normalized to  $\rm V_{DD}$   $$Low\ Power\ Design\ Techniques\ I$

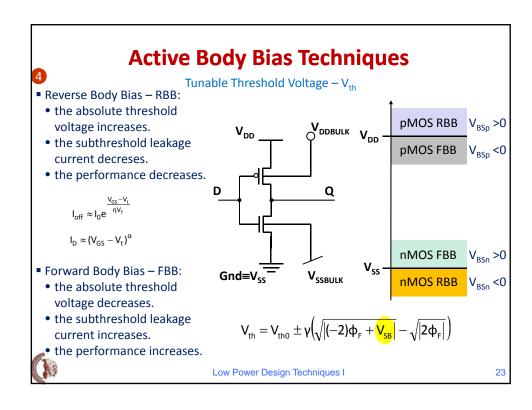

### **Reverse Body Bias**

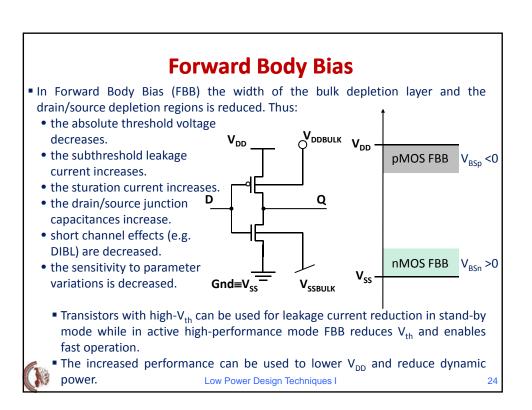

- In Reverse Body Bias (RBB) the width of the bulk depletion layer and the drain/source depletion regions is increased. Thus:

- the absolute threshold voltage increases.

- the subthreshold leakage current decreases.

- the sturation current decreases.

- the drain/source junction capacitances decreases.

- the sensitivity to parameter variations is increased.

Transistors with nominal V<sub>th</sub> can be used for high-performance operation while in stand-by mode RBB increases V<sub>th</sub> and reduces static power.

Low Power Design Techniques I

21

## **Variable Threshold Voltage V**<sub>th</sub>

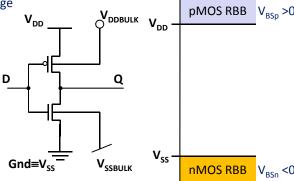

Reverse Body Bias – RBB

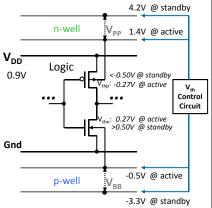

Substrate (body) voltage adaptation has been proposed, in order to increase the transistor threshold voltage in the idle state. In this state, the substrate of the pMOS transistors is biased to higher than  $V_{DD}$  voltage levels while the substrate of nMOS transistors is biased to negative voltage levels.

Thus, the weak inversion current is exponentially decreased, according to the pertinent expression, since the absolute threshold voltage  $V_{\text{th}}$  is increased.

Moreover, the DIBL current is also decreased.

$$V_{th} = V_{th0} \pm \gamma \left( \sqrt{\left| (-2)\varphi_{\scriptscriptstyle F} + \textcolor{red}{V_{\scriptscriptstyle SB}} \right|} - \sqrt{\left| 2\varphi_{\scriptscriptstyle F} \right|} \right)$$

$$\gamma = \frac{t_{ox}}{\epsilon_{ox}} \sqrt{2q\epsilon_{Si}N}$$

Variable threshold voltage – VTCMOS with Reverse Body (substrate) Bias – RBB

Kuroda et.al., IEEE J. Solid-State Circuits, 31(11), 1996

Low Power Design Techniques I

Low Power Design Techniques I

### References

- "Low Power Design Methodologies," J. Rabaey and M. Pedram, Springer, 1997.

- "Power Management of Digital Circuits in Deep Sub-Micron CMOS Technologies," S. Henzler, Springer, 2006.

- "Low-Power Digital VLSI Design," A. Bellaouar and M. Elmasry, Kluwer Academic Publishers, 1996.

- "A 1.5V Full-Swing Bootstrapped CMOS Large Capacitive-Load Driver Circuit Suitable for Low-Voltage CMOS VLSI," J. Lou and J. Kuo, IEEE Journal of Solid-State Circuits, vol. 32, no. 1, pp. 119-121, 1997.

- "A 0.9-V, 150-MHz, 10-mW, 4 mm, 2-D Discrete Cosine Transform Core Processor with Variable Threshold-Voltage (VT) Scheme," T. Kuroda et.al., IEEE Journal of Solid-State Circuits, vol. 31, no. 11, pp. 1770-1779, 1996.

- "Low-Power CMOS Digital Design," A. Chandrakasan, S. Sheng and R. Brodersen, IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, 1992.

- "Minimazing Power Consumption in Digital CMOS Circuits," A. Chandrakasan, R. Brodersen, Proceedings of the IEEE, vol. 83, no. 4, pp. 498-523, 1995.

Low Power Design Techniques I